|

Serial sequential adder

v.1.0

Example documentation project, author Vladimir Petrović

|

|

Serial sequential adder

v.1.0

Example documentation project, author Vladimir Petrović

|

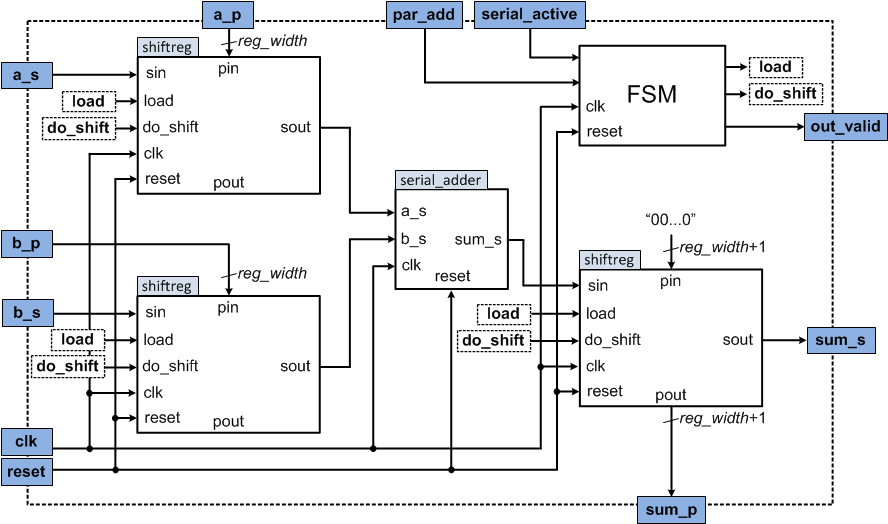

Behavioral architechture for serial_adder. More...

Processes | |

| fsm_adder_state_transition | ( clk , reset ) |

| fsm_adder_next_state_logic | ( state_reg , par_add , serial_active , timeout_counter ) |

| shift_reg_logic | ( state_reg , next_state , serial_active , timeout_counter ) |

| cnt_process | ( clk ) |

Components | |

| shiftreg | <Entity shiftreg> |

| serial_adder | <Entity serial_adder> |

Types | |

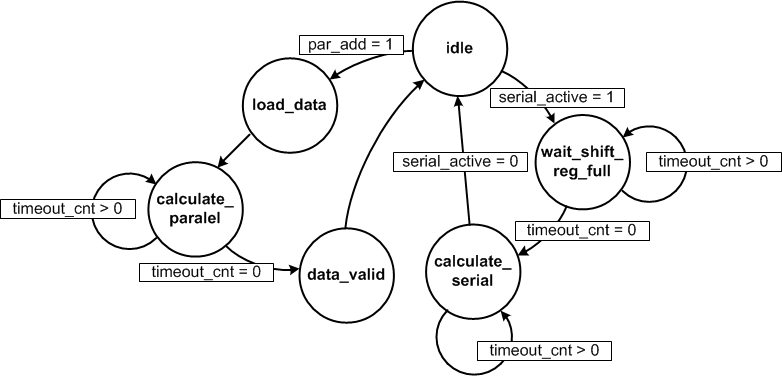

| state_type | ( idle , load_data , wait_shift_reg_full , calculate_paralel , data_valid_state , calculate_serial ) |

Signals | |

| state_reg | state_type |

| next_state | state_type |

| load | std_logic |

| do_shift | std_logic |

| a_s_out | std_logic |

| b_s_out | std_logic |

| sum_in | std_logic |

| generic_pin_for_sum_reg | std_logic_vector ( reg_width downto 0 ) |

| timeout_counter | integer range 0 to reg_width + 1 |

Instantiations | |

| shift_reg_a | shiftreg <Entity shiftreg> |

| shift_reg_b | shiftreg <Entity shiftreg> |

| shift_reg_sum | shiftreg <Entity shiftreg> |

| serial_adder_inst | serial_adder <Entity serial_adder> |

Sequential.....................

Definition at line 87 of file fsm_adder.vhd.

|

Process |

Definition at line 219 of file fsm_adder.vhd.

|

Process |

Definition at line 144 of file fsm_adder.vhd.

| fsm_adder_state_transition | ( | clk, | |

| reset | |||

| ) |

Definition at line 135 of file fsm_adder.vhd.

|

Process |

Definition at line 185 of file fsm_adder.vhd.

|

Signal |

Definition at line 120 of file fsm_adder.vhd.

|

Signal |

Definition at line 121 of file fsm_adder.vhd.

|

Signal |

Definition at line 119 of file fsm_adder.vhd.

|

Signal |

Definition at line 123 of file fsm_adder.vhd.

|

Signal |

Definition at line 118 of file fsm_adder.vhd.

|

Signal |

Definition at line 89 of file fsm_adder.vhd.

|

Component |

Definition at line 107 of file fsm_adder.vhd.

|

Instantiation |

Definition at line 133 of file fsm_adder.vhd.

|

Instantiation |

Definition at line 128 of file fsm_adder.vhd.

|

Instantiation |

Definition at line 129 of file fsm_adder.vhd.

|

Instantiation |

Definition at line 130 of file fsm_adder.vhd.

|

Component |

Definition at line 91 of file fsm_adder.vhd.

|

Signal |

Definition at line 89 of file fsm_adder.vhd.

|

Type |

Definition at line 88 of file fsm_adder.vhd.

|

Signal |

Definition at line 122 of file fsm_adder.vhd.

|

Signal |

Definition at line 125 of file fsm_adder.vhd.

1.8.12

1.8.12