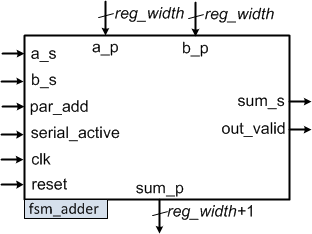

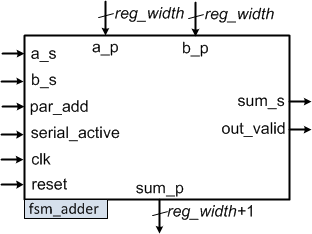

The fsm_adder is a sequential component that can serially add two binary numbers of any length. It has two input shift registers of width defined in generic reg_width and one output shift register of width reg_width+1 since the addition result is one bit longer than the addends. The interface description is shown in Fig. 1.

Fig. 1. A block symbol of the fsm_adder component

The component can work in two modes:

- Input numbers are loaded using the parallel load of two shift registers and output is stored in output shift register: When the signal par_add is equal to 1, fsm_adder should read the data from parallel input a_p and b_p and store the values to the input shift registers. In that case, addition starts immediatelly and after the output shift register is full, the result can be read from the sum_p parallel output. The fsm_adder generates a logical 1 at the out_valid output whenever the output value is valid.

- Input numbers are loaded serially via the a_s and b_s serial inputs, bit by bit at every rising edge of clk when the serial_active signal is equal to 1. After certain delay, output starts to show at the serial output sum_s. When the serial_active signal falls to 0, output can be generated but the data is no longer valid (out_valid is set to 0).

Definition at line 42 of file fsm_adder.vhd.

1.8.12

1.8.12