|

Serial sequential adder

v.1.0

Example documentation project, author Vladimir Petrović

|

|

Serial sequential adder

v.1.0

Example documentation project, author Vladimir Petrović

|

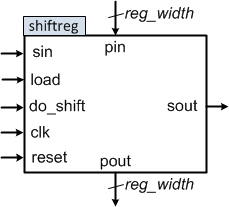

Entitiy declaration for shiftreg. More...

Entities | |

| shr_behav_arch | architecture |

| Behavioral architecture for shiftreg. More... | |

Libraries | |

| ieee | |

Use Clauses | |

| std_logic_1164 | |

| numeric_std | |

Generics | |

| reg_width | integer := 8 |

Ports | |

| clk | in std_logic |

| reset | in std_logic |

| load | in std_logic |

| do_shift | in std_logic |

| sin | in std_logic |

| sout | out std_logic |

| pin | in std_logic_vector ( reg_width - 1 downto 0 ) |

| pout | out std_logic_vector ( reg_width - 1 downto 0 ) |

The shift register has a generic reg_width which defines the width of the shift register. Shift register can have two input modes, serial input and paralel input. Register shifts data from serial input sin if the do_shift is 1. After the register is full, first input bit is shown at serial output sout. The shift register has parallel output pout too. If the load signal is active, parallel load is active where the data form input pin is stored in the register. Under reset, all flipflops in shifreg are set to 0. shiftreg's interface is shown in Fig. 1.

Definition at line 32 of file shiftreg.vhd.

|

Port |

Definition at line 37 of file shiftreg.vhd.

|

Port |

Definition at line 39 of file shiftreg.vhd.

|

Library |

Definition at line 19 of file shiftreg.vhd.

|

Port |

Definition at line 39 of file shiftreg.vhd.

|

Package |

Definition at line 22 of file shiftreg.vhd.

Definition at line 42 of file shiftreg.vhd.

Definition at line 44 of file shiftreg.vhd.

|

Generic |

Definition at line 35 of file shiftreg.vhd.

|

Port |

Definition at line 38 of file shiftreg.vhd.

|

Port |

Definition at line 40 of file shiftreg.vhd.

|

Port |

Definition at line 41 of file shiftreg.vhd.

|

Package |

Definition at line 21 of file shiftreg.vhd.

1.8.12

1.8.12