|

Serial sequential adder

v.1.0

Example documentation project, author Vladimir Petrović

|

|

Serial sequential adder

v.1.0

Example documentation project, author Vladimir Petrović

|

Behavioral and structural architechture for serial_adder. More...

Processes | |

| serial_adder_state_transition | ( reset , clk ) |

| State transition process. When reset is active state machine is in the cout_0 state. | |

| serial_adder_next_state_logic | ( carry_out ) |

| Next state process. When calculated carry is 0 the next state is cout_0 state, otherwise the next state is cout_1 state. | |

Components | |

| fulladder | <Entity fulladder> |

Types | |

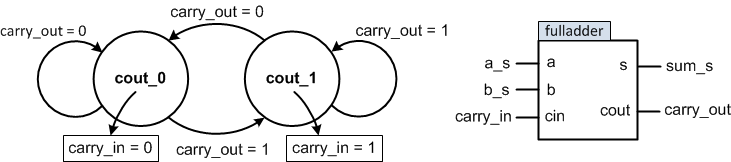

| state_type | ( cout_0 , cout_1 ) |

| Definition of states of serial_adder state machine. See detailed description for more details. | |

Signals | |

| state_reg | state_type |

| next_state | state_type |

| carry_out | std_logic |

| carry_in | std_logic |

Instantiations | |

| fa | fulladder <Entity fulladder> |

Serial adder is realized as simple state machine shown in Fig. 1. It has two states, cout_0 and cout_1. For binary addition serial adder instantiates fulladder component and its inputs are serial inputs a_s and b_s, while its output sum is sum_s. Input signals change at every rising edge of clk signal. Input carry should be the output carry from previous calculation. Input carry is determined by the current state of the state machine. These states define two possible situations: cout_0 is the state when input carry (previous output carry) is equal to 0, while cout_1 is the state when input carry (previous output carry) is equal to 1.

Definition at line 54 of file serial_adder.vhd.

|

Process |

Definition at line 92 of file serial_adder.vhd.

| serial_adder_state_transition | ( | reset, | |

| clk | |||

| ) |

Definition at line 82 of file serial_adder.vhd.

|

Signal |

Definition at line 63 of file serial_adder.vhd.

|

Signal |

Definition at line 62 of file serial_adder.vhd.

|

Instantiation |

Definition at line 79 of file serial_adder.vhd.

|

Component |

Definition at line 66 of file serial_adder.vhd.

|

Signal |

Definition at line 60 of file serial_adder.vhd.

|

Signal |

Definition at line 60 of file serial_adder.vhd.

|

Type |

Definition at line 57 of file serial_adder.vhd.

1.8.12

1.8.12