|

Serial sequential adder

v.1.0

Example documentation project, author Vladimir Petrović

|

|

Serial sequential adder

v.1.0

Example documentation project, author Vladimir Petrović

|

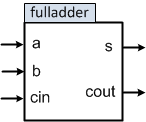

Entitiy declaration for fulladder. More...

Entities | |

| fa_behav | architecture |

| Behavioral architechture for fulladder. More... | |

Libraries | |

| ieee | |

Use Clauses | |

| std_logic_1164 | |

Ports | |

| a | in std_logic |

| Input bit 1. | |

| b | in std_logic |

| Input bit 2. | |

| cin | in std_logic |

| Input carry. | |

| s | out std_logic |

| Output sum. | |

| cout | out std_logic |

| Output carry. | |

Full adder is a simple combinational circuit that adds two input signals a and b and an input carry signal cin to a sum s and output carry signal cout. Fulladder's interface is shown in Fig. 1.

Definition at line 18 of file fulladder.vhd.

|

Port |

Definition at line 22 of file fulladder.vhd.

|

Port |

Definition at line 24 of file fulladder.vhd.

|

Port |

Definition at line 26 of file fulladder.vhd.

|

Port |

Definition at line 32 of file fulladder.vhd.

|

Library |

Definition at line 1 of file fulladder.vhd.

|

Port |

Definition at line 29 of file fulladder.vhd.

|

Package |

Definition at line 2 of file fulladder.vhd.

1.8.12

1.8.12