**Federal University of Santa Catarina**

Center for Technology Computer Science & Electronics Engineering

# **Integrated Circuits & Systems**

#### **INE 5442**

#### Lecture 18 CMOS Sequential Circuits - 1

Prof. José Luís Güntzel guntzel@inf.ufsc.br

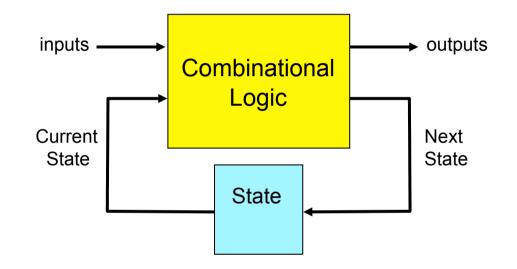

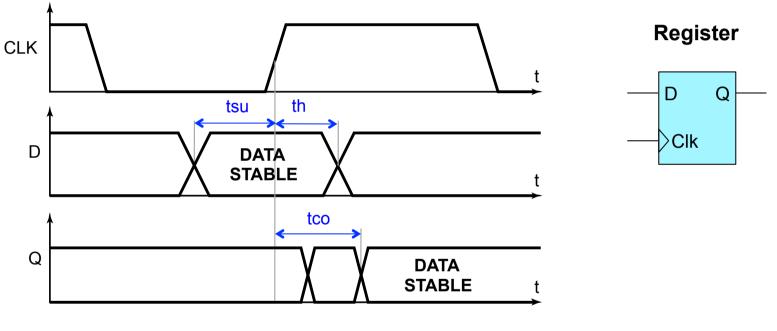

#### **Sequential Logic**

2 Storage Mechanisms:Positive feedbackCharge Based

Source: Rabaey; Chandrakasan; Nikolic, 2003

**INE/CTC/UFSC** Integrated Circuits and Systems

Slide 18.2

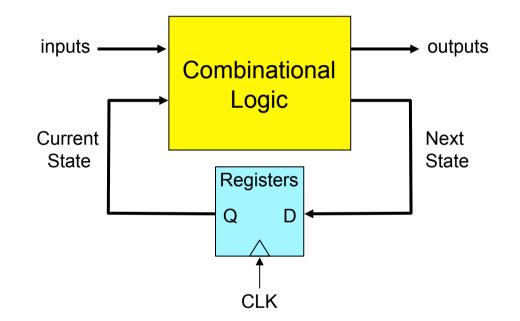

#### **Sequential Logic**

#### **Positive Feedback: uses latches or registers**

#### **Naming Conventions**

#### In Rabaey's IC book:

- A latch is level sensitive

- A register is edge-triggered

#### Many other books:

Flip-flop is an edge-triggered

Source: Rabaey; Chandrakasan; Nikolic, 2003

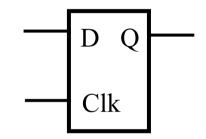

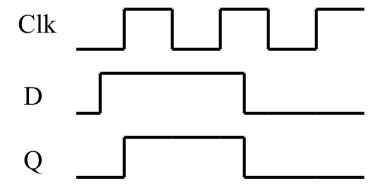

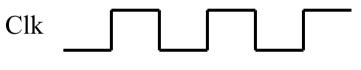

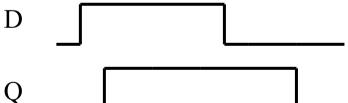

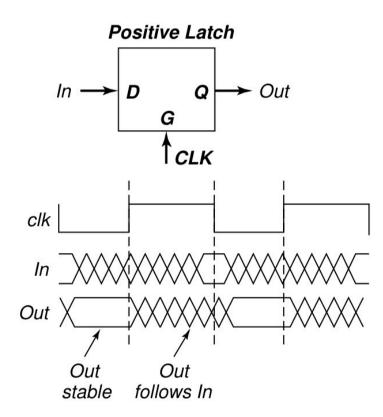

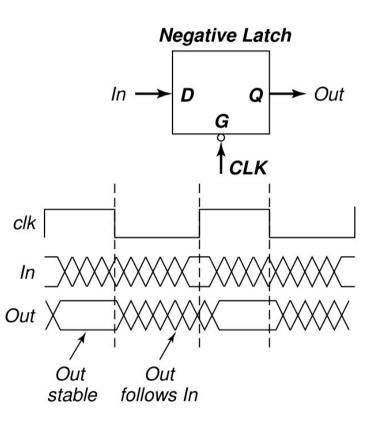

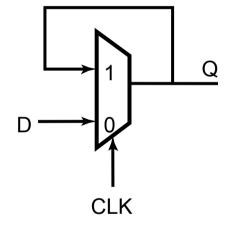

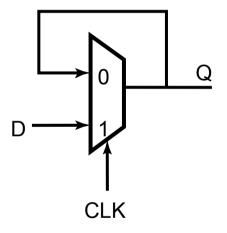

#### **Latch Versus Register**

□ Latch

stores data when clock is low

#### Register

stores data when clock rises

Source: Rabaey; Chandrakasan; Nikolic, 2003

**INE/CTC/UFSC** Integrated Circuits and Systems

Slide 18.5

**Latches**

Source: Rabaey; Chandrakasan; Nikolic, 2003

**INE/CTC/UFSC** Integrated Circuits and Systems

Slide 18.6

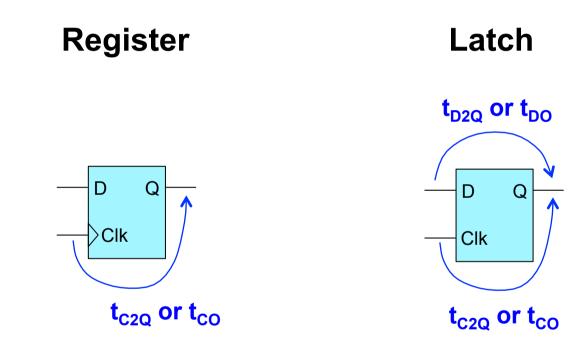

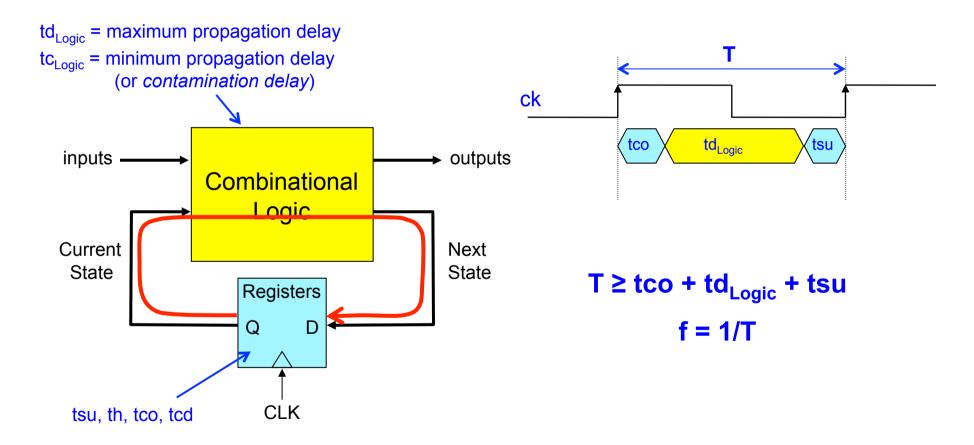

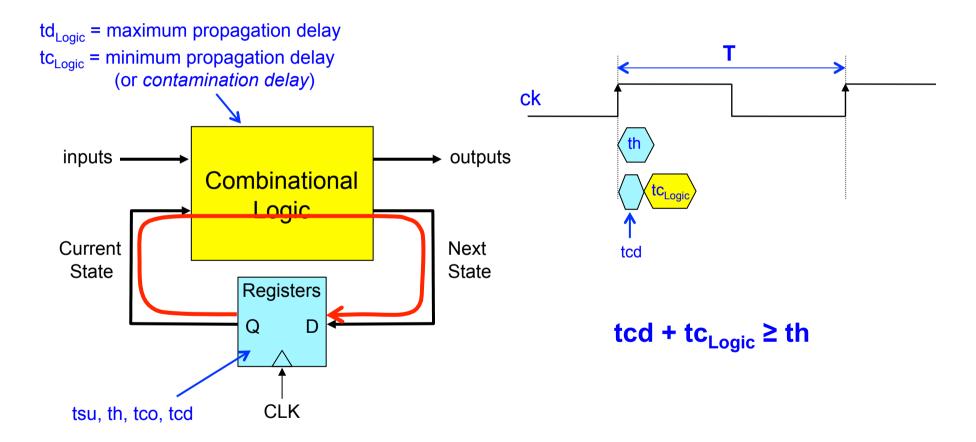

### **Timing Definitions**

tsu = setup time

th = hold time

tco = tc2q = maximum propagation delay (or time from clock to output Q)

tcd = minimum propagation delay (or *contamination delay*)

Source: Rabaey; Chandrakasan; Nikolic, 2003

**INE/CTC/UFSC** Integrated Circuits and Systems

Slide 18.8

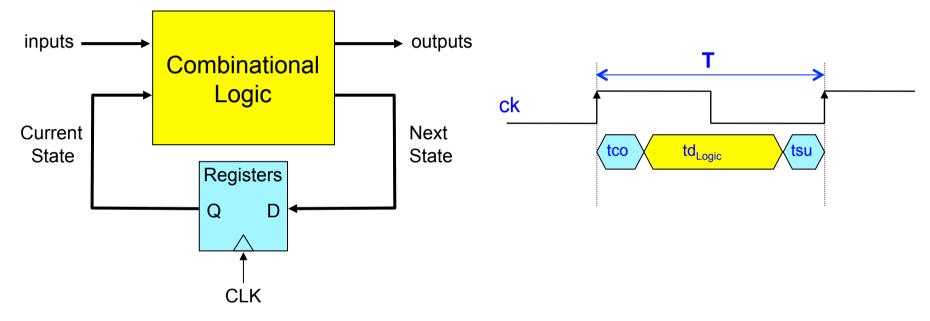

#### **Maximum Clock Frequency**

#### **Avoiding Race Condition**

#### **Maximum Clock Frequency**

In contemporary designs:

□ The maximum logic depth is around 12 gates

□ Approx. 15% of the clock period is due to register overheads

□ tcd + tc<sub>Logic</sub> ≥ th is quite easy to meet if clock slew can be disregarded

**INE/CTC/UFSC** Integrated Circuits and Systems

Slide 18.11

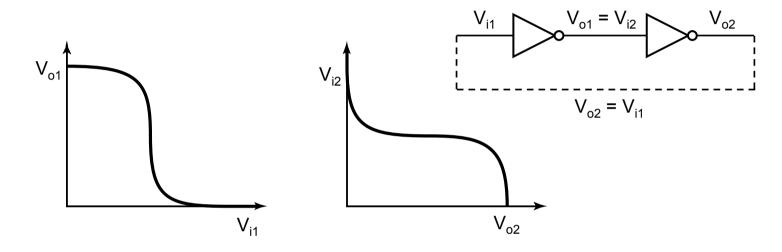

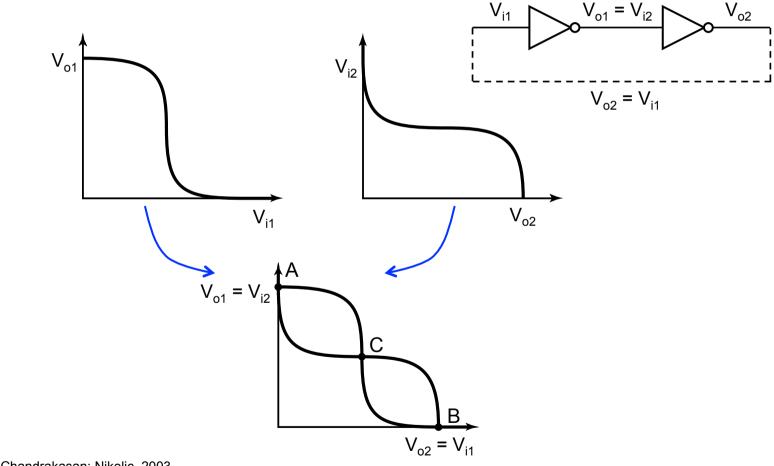

#### **Positive Feedback: Bi-Stability**

Source: Rabaey; Chandrakasan; Nikolic, 2003

**INE/CTC/UFSC** Integrated Circuits and Systems

#### **Positive Feedback: Bi-Stability**

Source: Rabaey; Chandrakasan; Nikolic, 2003

INE/CTC/UFSC Integrated Circuits and Systems

Slide 18.13

#### **Meta-Stability**

#### G is the loop gain

Source: Rabaey; Chandrakasan; Nikolic, 2003

#### **INE/CTC/UFSC** Integrated Circuits and Systems

Slide 18.14

### **Changing the State of a Bistable**

#### Cutting the feedback loop:

- Multiplexer-based structure

- Once the loop is open, a new value can be easily written in

- This is the most popular approach in today's latches

#### Overpowering the feedback loop:

- By applying a trigger signal at the input of the bistable a new value is forced into the cell

- Careful sizing of the transistors in the feedback loop and trigger circuitry

- Currently, is used to built static background memories

$$Q = Clk \cdot Q + \overline{Clk} \cdot D$$

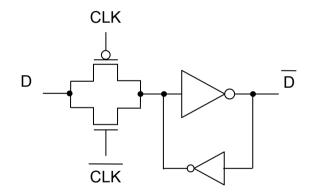

#### Writing into a Static Latch

Use the clock as a decoupling signal, that distinguishes between the transparent and opaque states

| CLK |  |

|-----|--|

| CLK |  |

#### **Converting into a MUX**

#### Writing into a Static Latch

Use the clock as a decoupling signal, that distinguishes between the transparent and opaque states

#### **Converting into a MUX**

#### Writing into a Static Latch

Use the clock as a decoupling signal, that distinguishes between the transparent and opaque states

Forcing the state

# If the transmission gate has minimum sized transistors, the lower inverter must be even weaker!

Slide 18.18

#### Writing into a Static Latch

Use the clock as a decoupling signal, that distinguishes between the transparent and opaque states

Forcing the state

#### Writing into a Static Latch

#### **Converting into a MUX**

#### Forcing the state

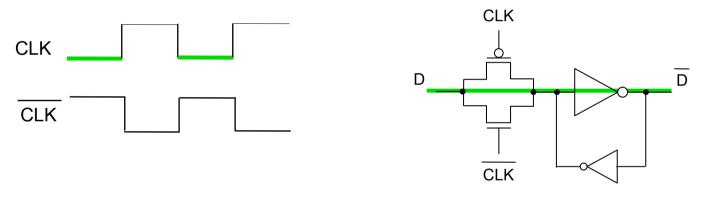

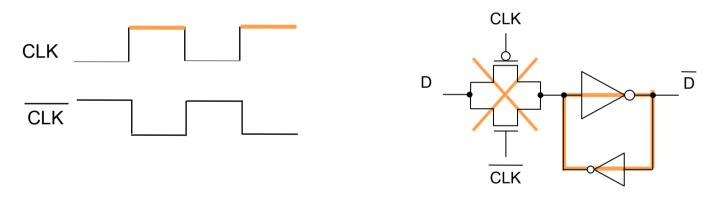

#### **Mux-Based Latches**

**Negative latch** (transparent when CLK= 0)

Positive latch (transparent when CLK= 1)

$Q = Clk \cdot Q + \overline{Clk} \cdot D$

$Q = \overline{Clk} \cdot Q + Clk \cdot D$

Source: Rabaey; Chandrakasan; Nikolic, 2003

**INE/CTC/UFSC** Integrated Circuits and Systems

Slide 18.21

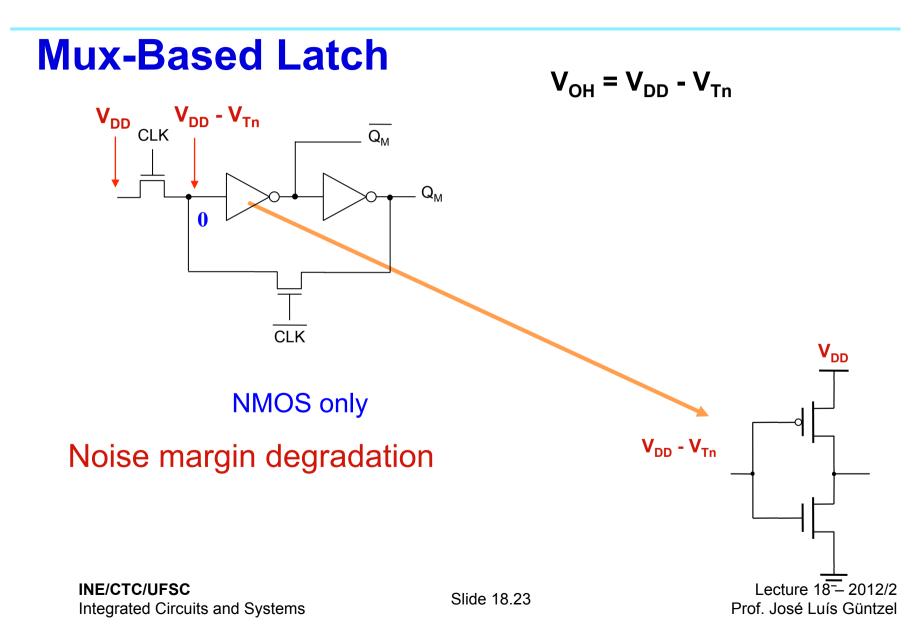

#### **Mux-Based Latch**

$$P = \alpha_{0 \to 1} \cdot C_L \cdot VDD^2 \cdot f$$

CLK: α<sub>0→1</sub> = 1

#### How many transistor loads seen by CLK per bit?

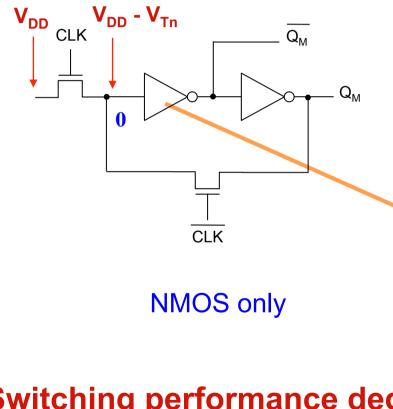

#### **Mux-Based Latch**

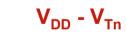

$t_{pHL} \approx 0.69 R_{eq-NMOS} C_L$  $\mathbf{R}_{eq} \approx (\mathbf{R}_{on}(\mathbf{t}_1) + \mathbf{R}_{on}(\mathbf{t}_2))/2$  $\mathbf{R}_{on}(t) \approx \mathbf{V}_{DS}(t) / \mathbf{I}_{D}(t)$  $I_D \approx \frac{k'_n}{2} \frac{W}{L} (V_{GS} - V_T)^2$  $\mathbf{V}_{\mathsf{D}\mathsf{D}}$

#### Switching performance degradation

**INE/CTC/UFSC** Integrated Circuits and Systems

#### **Mux-Based Latch**

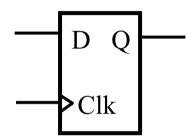

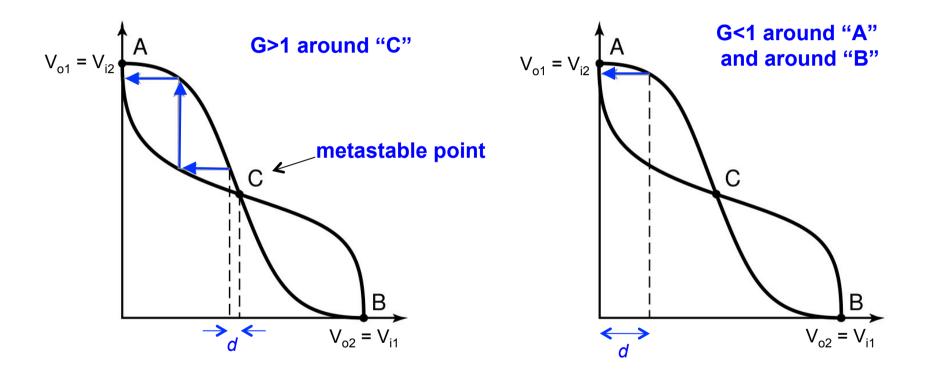

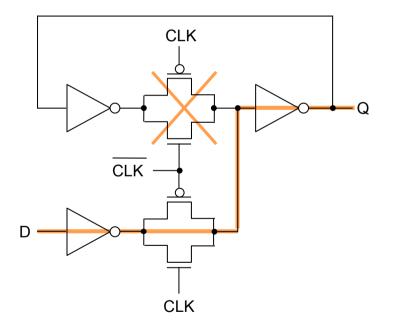

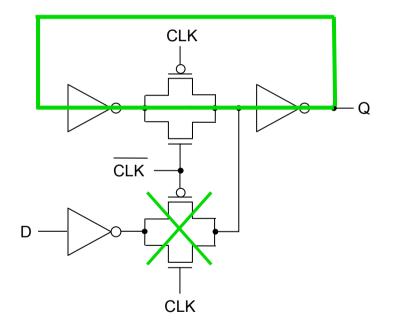

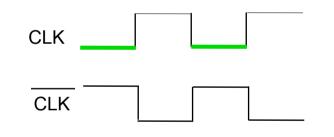

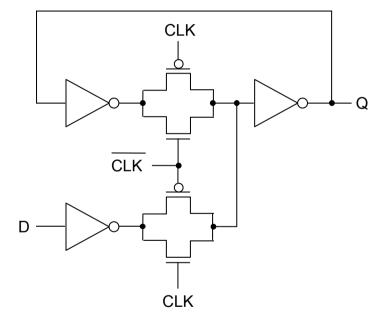

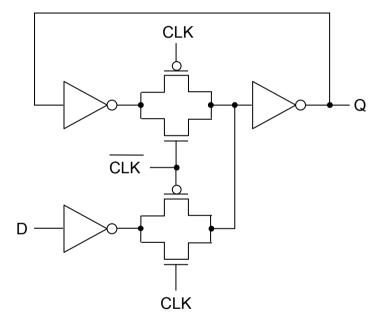

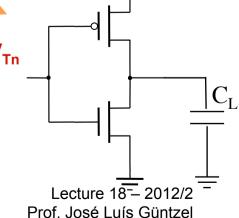

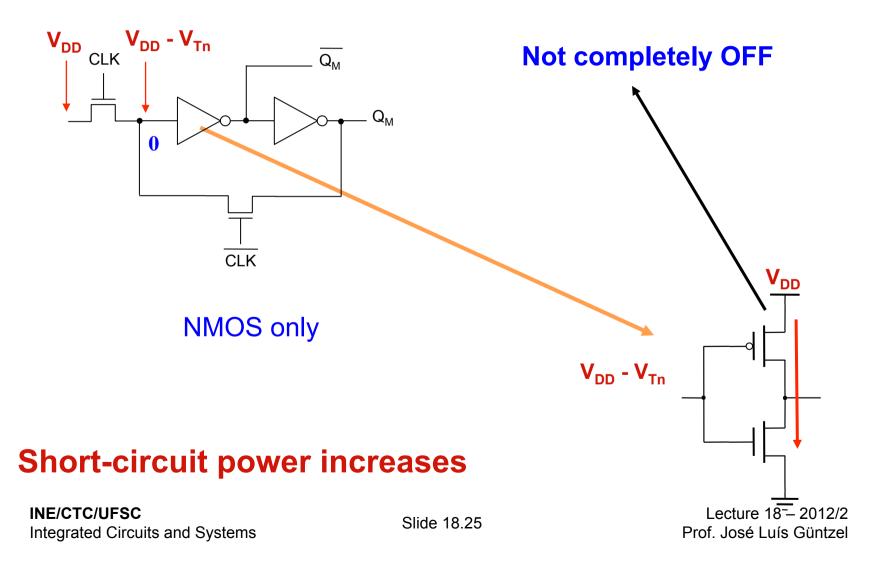

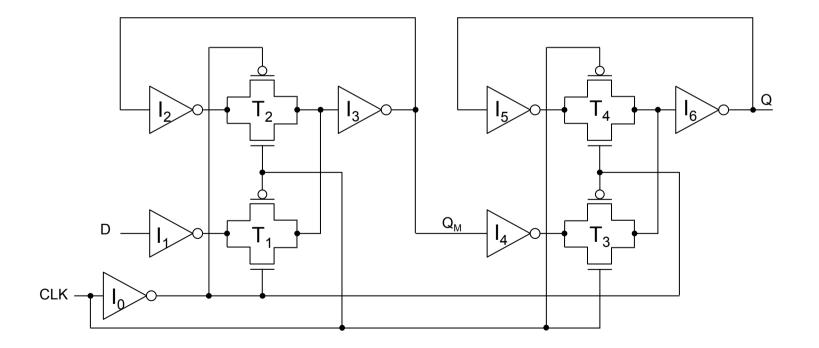

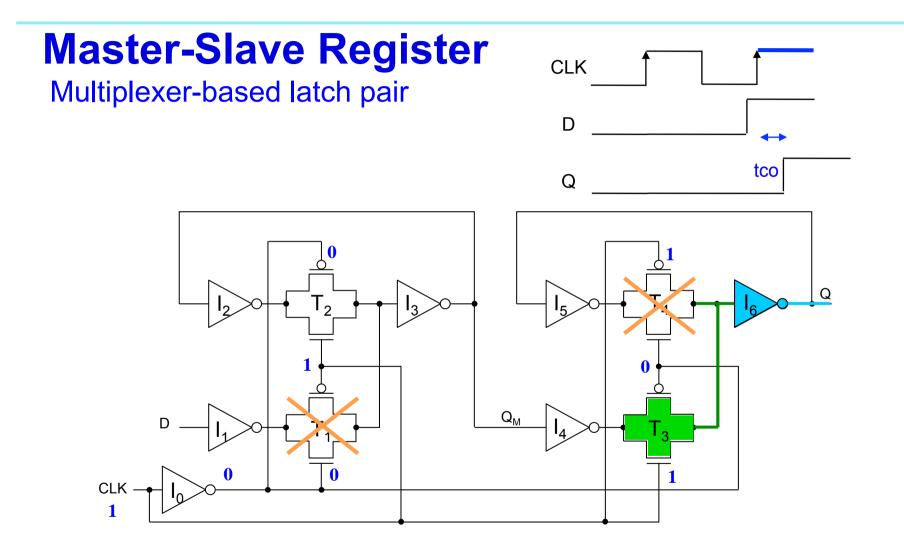

### Master-Slave (Edge-Triggered) Register

#### Two opposite latches trigger on edge Also called master-slave latch pair

Source: Rabaey; Chandrakasan; Nikolic, 2003

**INE/CTC/UFSC** Integrated Circuits and Systems

Slide 18.26

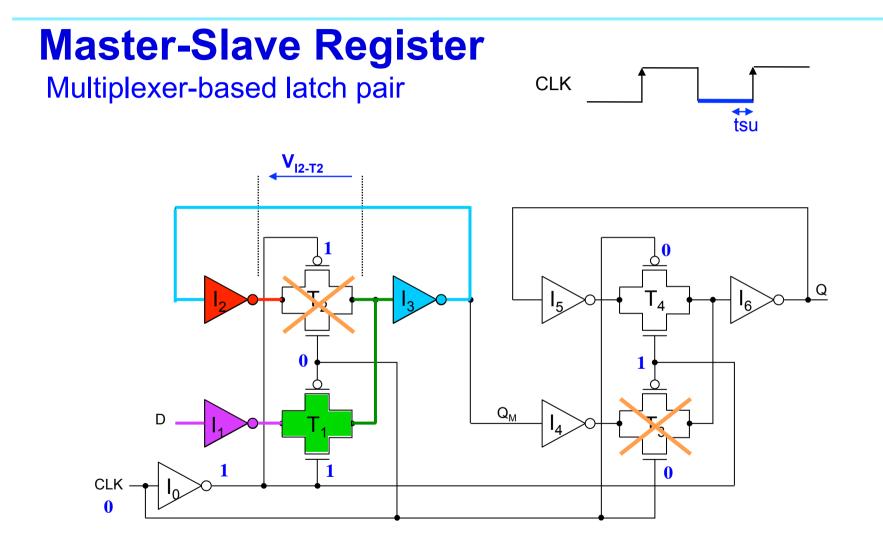

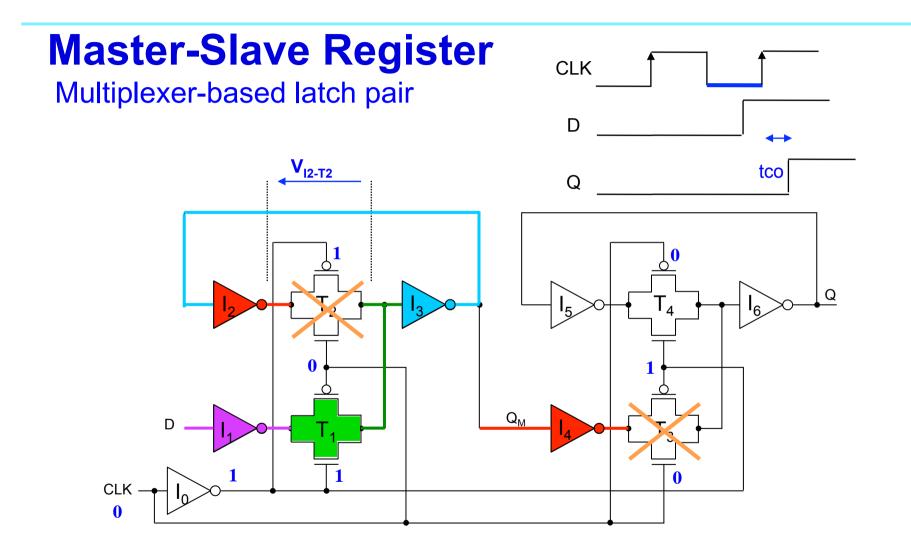

#### **Master-Slave Register**

Multiplexer-based latch pair

**INE/CTC/UFSC** Integrated Circuits and Systems

Slide 18.27

**INE/CTC/UFSC** Integrated Circuits and Systems

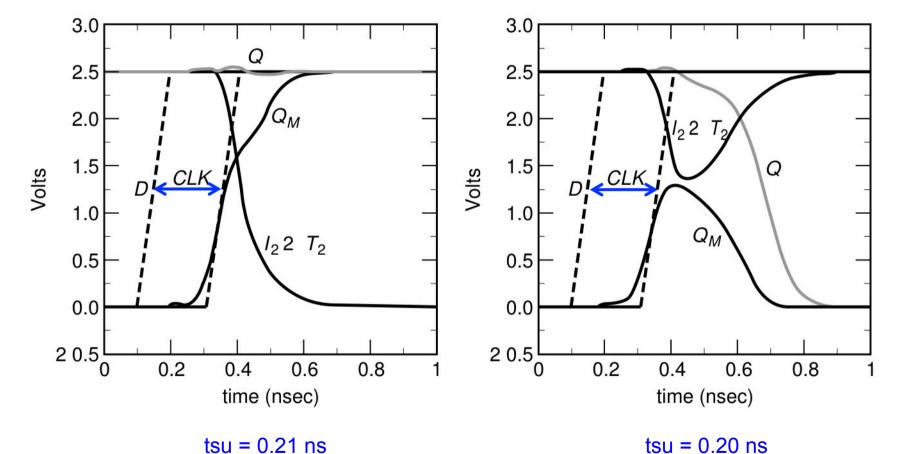

#### **Setup Time**

tsu = 0.21 ns

Source: Rabaey; Chandrakasan; Nikolic, 2003

#### **INE/CTC/UFSC**

Integrated Circuits and Systems

Slide 18.29

**INE/CTC/UFSC** Integrated Circuits and Systems

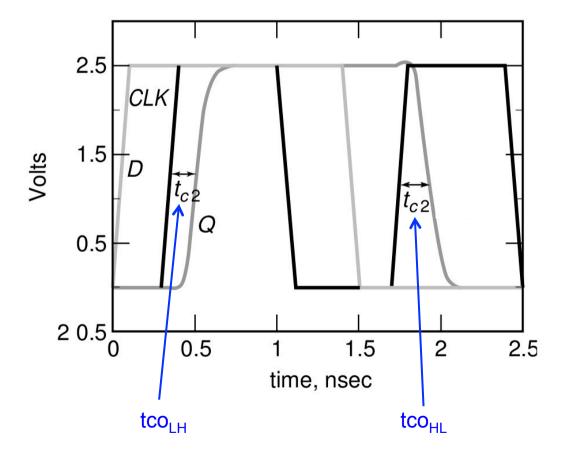

#### **Clk to Output (Q) Delay**

Source: Rabaey; Chandrakasan; Nikolic, 2003

#### INE/CTC/UFSC

Integrated Circuits and Systems

Slide 18.32

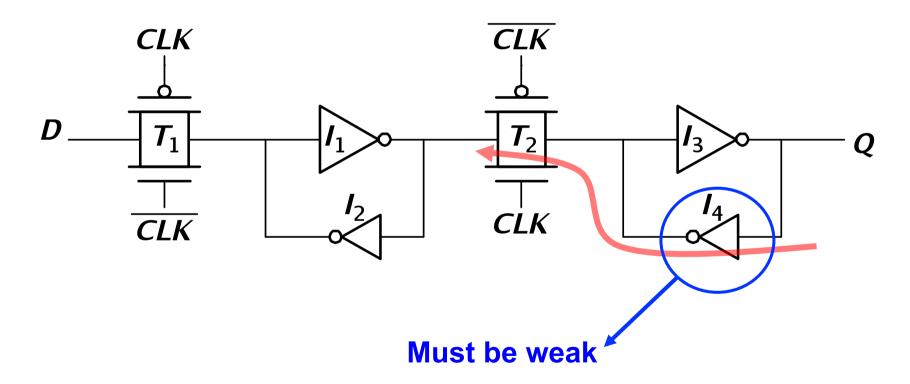

#### **Reduced Clock Load Master-Salve Register**

Source: Rabaey; Chandrakasan; Nikolic, 2003

#### INE/CTC/UFSC

Integrated Circuits and Systems

Slide 18.33

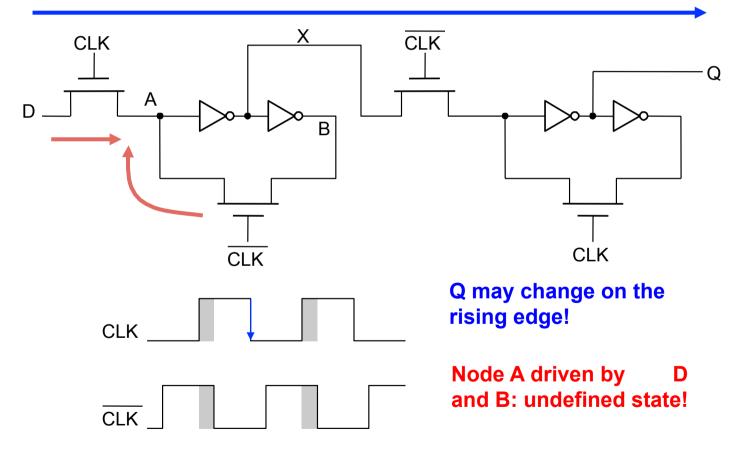

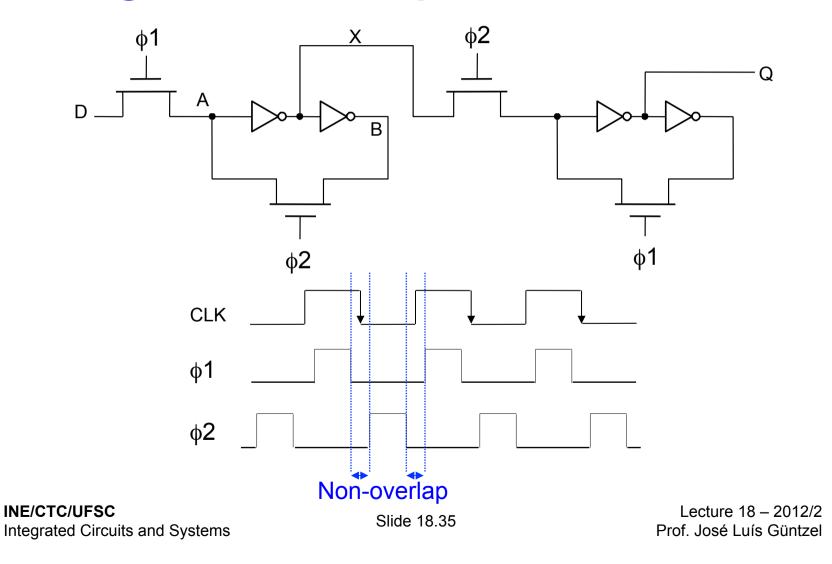

#### **Avoiding Clock Overlap**

Source: Rabaey; Chandrakasan; Nikolic, 2003

**INE/CTC/UFSC** Integrated Circuits and Systems

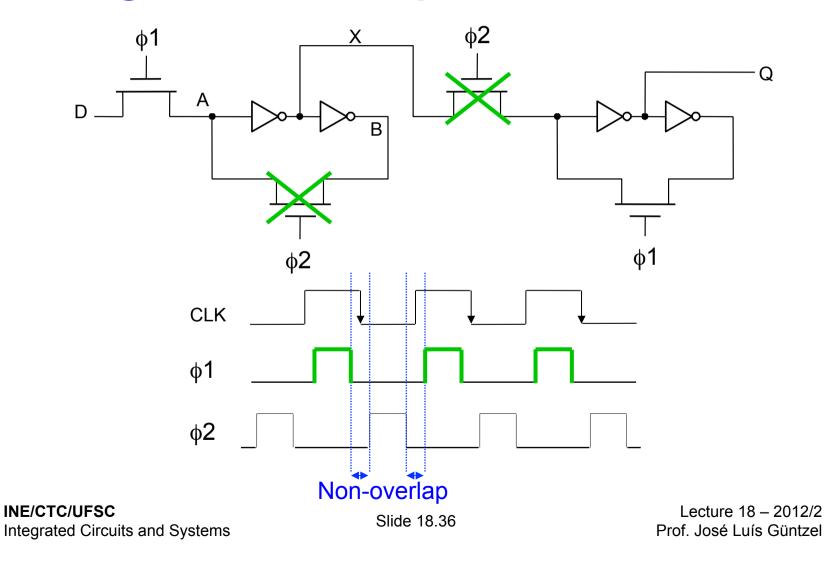

#### **Avoiding Clock Overlap**

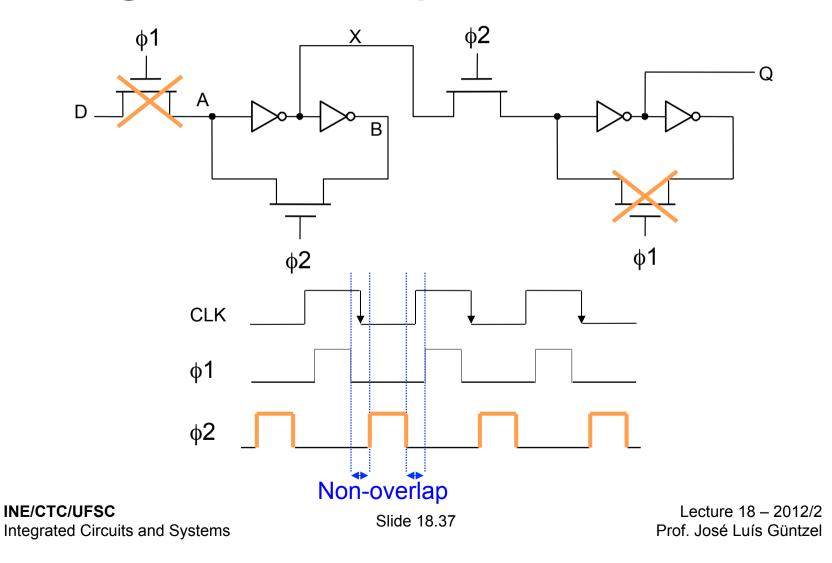

#### **Avoiding Clock Overlap**

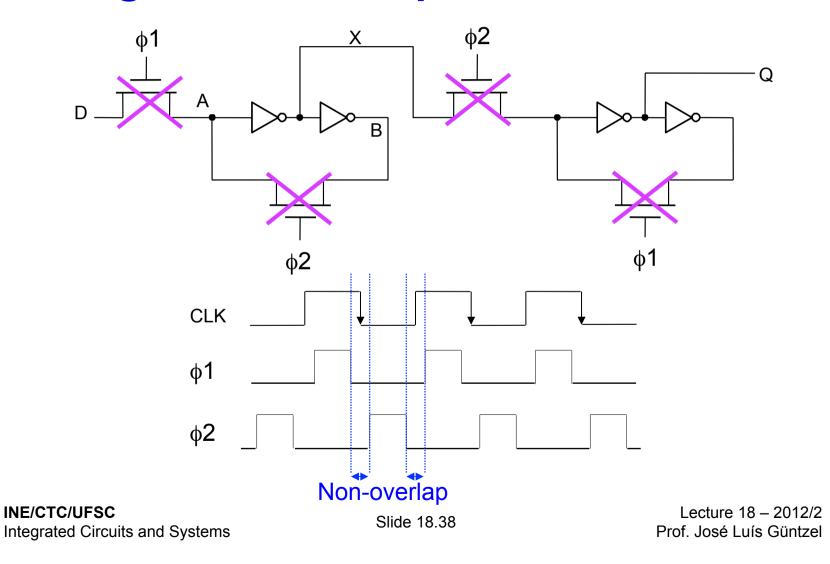

#### **Avoiding Clock Overlap**

#### **Avoiding Clock Overlap**

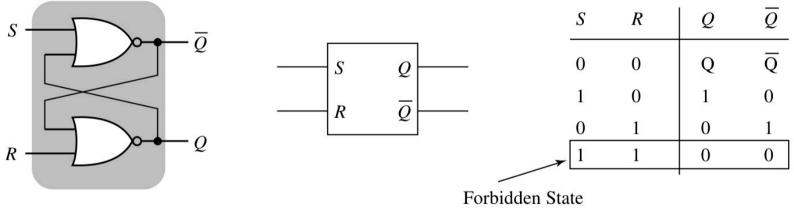

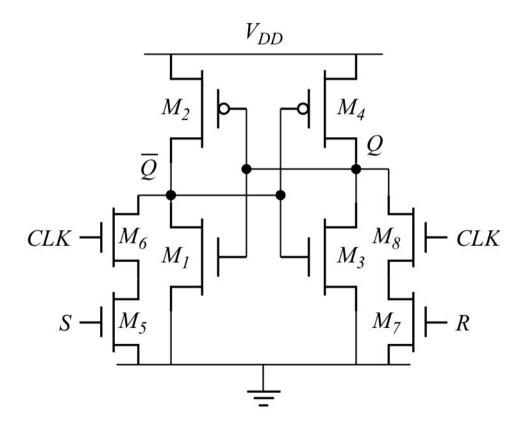

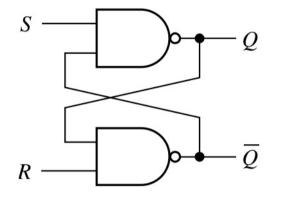

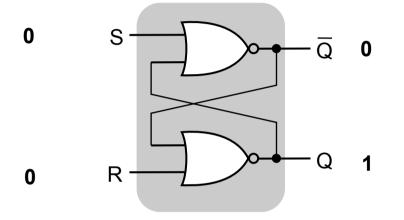

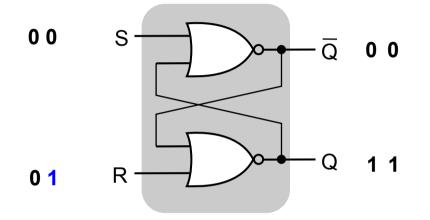

# **Overpowering the Feedback Loop – Cross-Coupled Pairs**

#### **NOR-based set-reset**

Source: Rabaey; Chandrakasan; Nikolic, 2003

#### Asynchronous doesn't fit in dominant methodology! (99% of the ICs are synchronous)

#### How to turn it into a synchronous circuit?

INE/CTC/UFSC Integrated Circuits and Systems

Slide 18.39

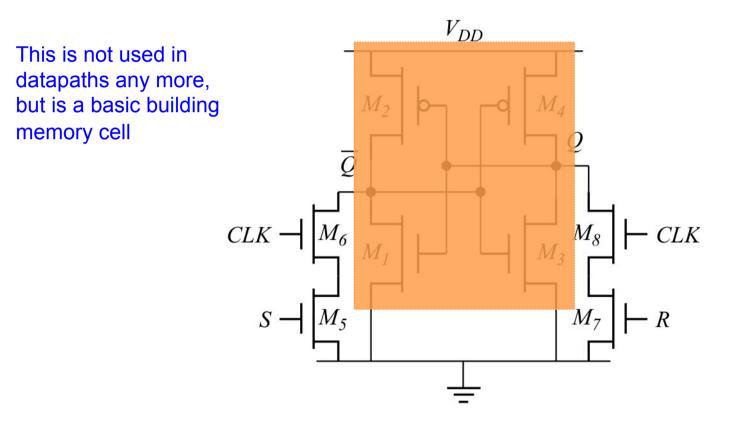

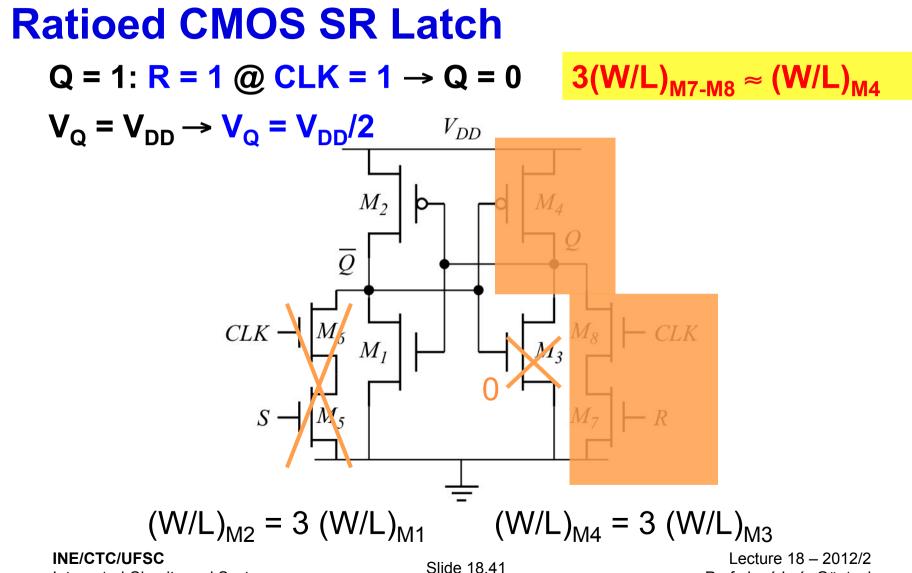

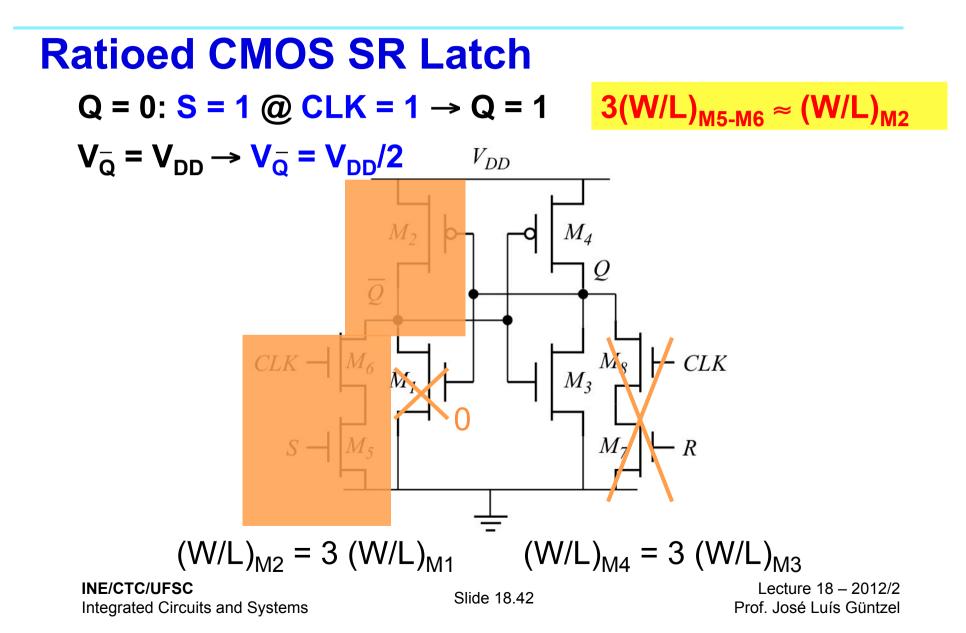

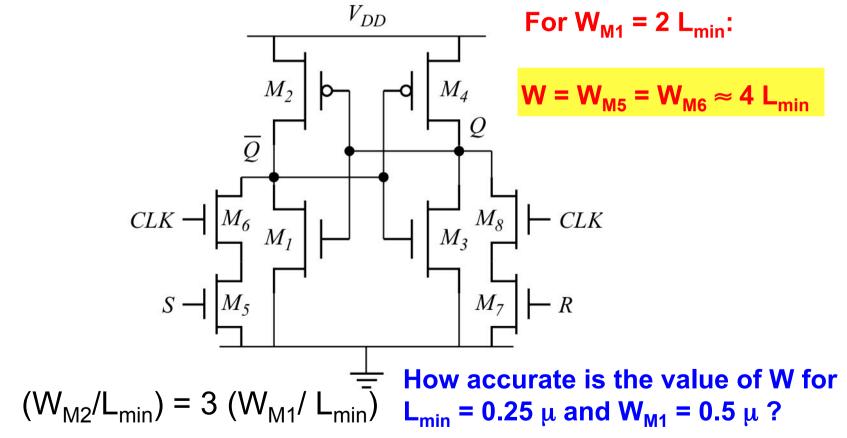

#### **Ratioed CMOS SR Latch**

$$(W/L)_{M2} = 3 (W/L)_{M1} (W/L)_{M4} = 3 (W/L)_{M3}$$

**INE/CTC/UFSC** Integrated Circuits and Systems

Slide 18.40

Integrated Circuits and Systems

Prof. José Luís Güntzel

#### **Ratioed CMOS SR Latch**

$3(W/L)_{M5-M6} \approx (W/L)_{M2} = (W_{M2}/L_{min}) = (3W_{M1}/L_{min})$  $V_{DD}$  $(W/L)_{M5-M6} = W/(2 L_{min})$  $M_4$  $\mathbf{W} = \mathbf{W}_{M5} = \mathbf{W}_{M6}$  $M_2$ Q  $\overline{Q}$  $M_8$ CLK CLK  $M_3$  $M_1$  $M_7$  $M_5$  $S \cdot$ -R $(W_{M2}/L_{min}) = 3 (W_{M1}/L_{min})$

**INE/CTC/UFSC** Integrated Circuits and Systems

Slide 18.43

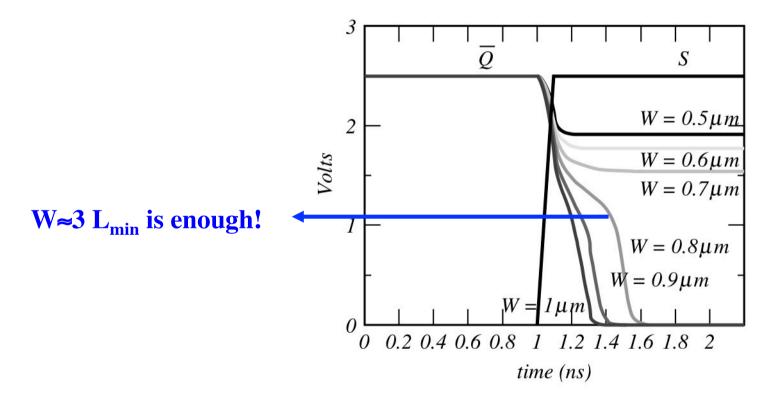

#### Ratioed CMOS SR Latch 3(W/L)<sub>M5-M6</sub> ≈ 3 W/(2 L<sub>min</sub>) = 3 W<sub>M1</sub>/L<sub>min</sub>

**INE/CTC/UFSC** Integrated Circuits and Systems

Slide 18.44

#### **Ratioed CMOS SR Latch Sizing Issues**

#### **Transient response**

#### **Synchronized Cross-Coupled NAND**

#### Requires proper transitor sizing: ratioed design.

**INE/CTC/UFSC** Integrated Circuits and Systems

Slide 18.46

#### **Cross-Coupled NAND**

What is the corresponding truth table?

For a given tp, which requires more area synchronized cross-coupled NOR or NAND?

**INE/CTC/UFSC** Integrated Circuits and Systems

Slide 18.47

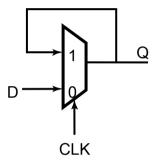

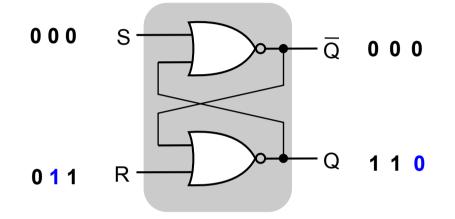

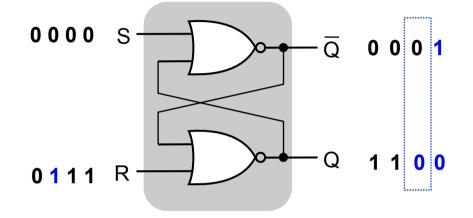

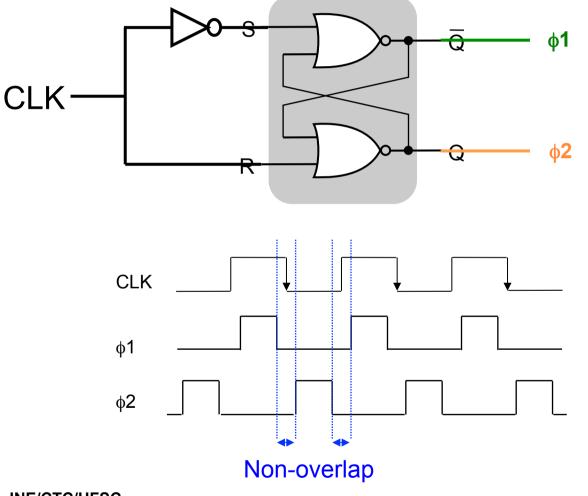

**Generating Two-Phase Non-Overlapping Clock**

**Initial Values**

**Generating Two-Phase Non-Overlapping Clock**

Time =  $t_o$

**Generating Two-Phase Non-Overlapping Clock**

Time =  $t_0 + d$

**Generating Two-Phase Non-Overlapping Clock**

Time =  $t_0$  + 2d

**Generating Two-Phase Non-Overlapping Clock**

**INE/CTC/UFSC** Integrated Circuits and Systems

Slide 18.52

# References

- RABAEY, J; CHANDRAKASAN, A.; NIKOLIC, B. Digital Integrated Circuits: a design perspective. 2<sup>nd</sup> Edition. Prentice Hall, 2003. ISBN: 0-13-090996-3.

- WESTE, Neil; HARRIS, David. CMOS VLSI Design: a circuits and systems perspective. Addison-Wesley, 4<sup>th</sup> Edition, 2010. ISBN 978-0321547743.