# **Rail-to-Rail OTA**

Radivoje Đurić, 2015, Analogna Integrisana Kola

## □ Rail-to-rail CMOS op amp

•Generally, rail-to-rail amplifiers are useful in low-voltage applications, where it is necessary to efficiently use the limited span offered by the power supply.

•While conventional amplifiers are capable of linear operation only for signals with a small excursion around the common-mode levels, rail-to-rail amplifiers are designed to allow signals to swing within millivolts of either power supply rail.

•The input and output voltage ranges are dependent on the amplifier topology, and the rail-torail operation can be achieved for either the input or the output, or both input and output

#### CMOS amplifier with rail-to-rail input

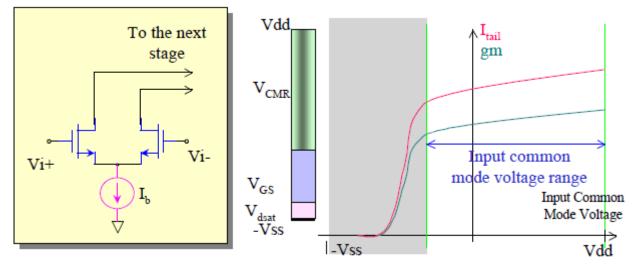

#### •NMOS differential pair

Radivoje Đurić, 2015, Analogna Integrisana Kola

•PMOS differential pair

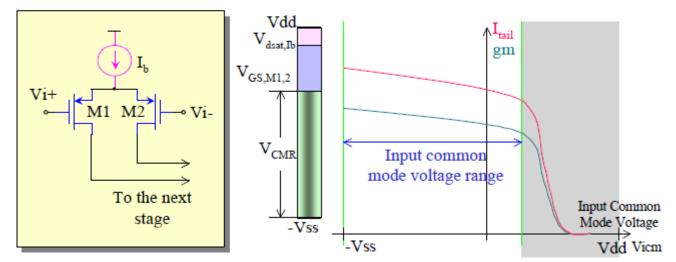

•PMOS+NMOS differential pair

Radivoje Đurić, 2015, Analogna Integrisana Kola

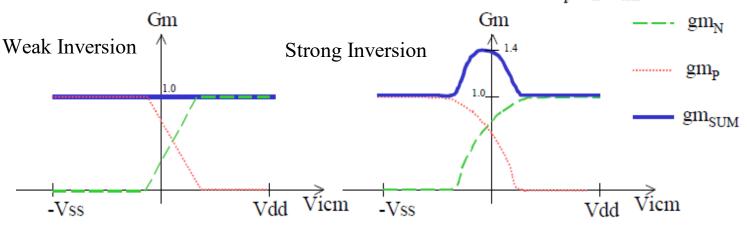

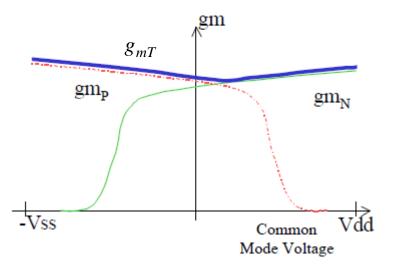

•Due to the different dc behavior of each pair, the resulting transconductance varies with the common-mode input voltage and is not constant.

•When the common-voltage, vCM, is at mid-rail, both n- and p-channel transistor stages operate normally, as a result, the total transconductance gmT, which is about two times greater than that obtained in the cases where vCM is close to either of the supply voltages, VSS or VDD, and only one pair type remains

operational.

•This transconductance variation can be efficiently reduced by using differential pairs based on improved biasing circuits

Radivoje Đurić, 2015, Analogna Integrisana Kola

### Techniques for N-P Complementary Rail-to-Rail Input Stage

1. For input stages with input transistors working in weak-inversion region, using current complementary circuit to keep the sum of In and Ip constant

Basic idea:

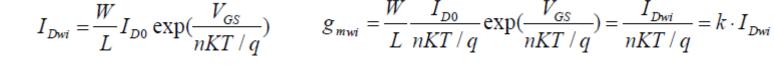

•For CMOS transistors working in weak-inversion region

• So, the total transconductance of the input stage is

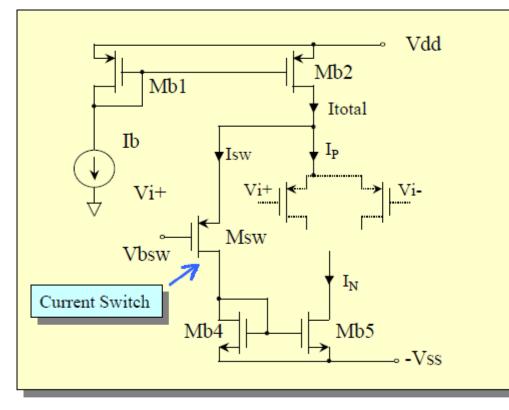

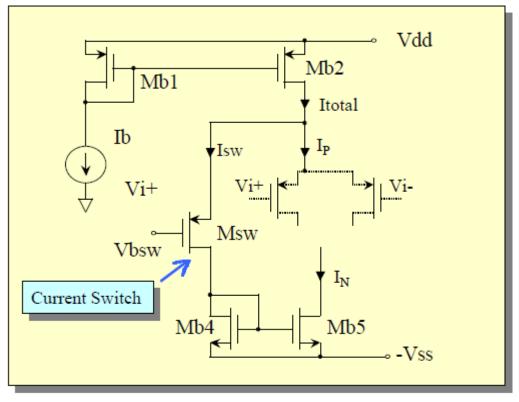

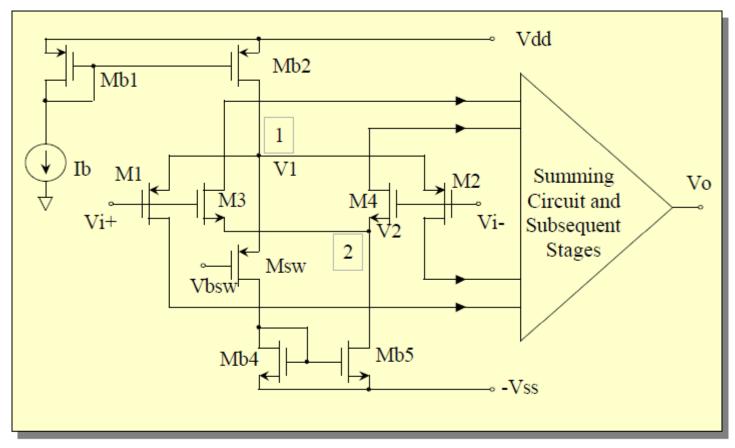

$g_{mT} = g_{mN} + g_{mP} = k(I_N + I_P)$ Thus the transconductance of the input stage is proportional to the sum of the tail currents of N and P pairs. •Mb4 and Mb5 mirror the current through Msw, Isw, to provide the tail current of the N-channel input pair. Mb4 and Mb5 are with the same geometry.

•Mb2 always works in saturation region, and never to ohmic region, by properly selecting the gate biasing voltage Vbsw of Msw. •Msw works as a current switch

✓When the input common mode voltage, Vicm, is close to Vdd, the P input pair cuts off, the drain current of Mb2, Itotal is diverted to Msw. And then mirrored through Mb4 and Mb5, to the source node of the N input pair.

✓When Vicm is close to -Vss, the switch Msw cuts off, Itotal then flows to the P input pair.

✓ In between, part of Itail flows to P pair, and the rest to Msw, through current mirror Mb4 and Mb5, to the N pair.

•Using a first order approximation, the following equation stands,  $I_p+I_n=I_{tail}=const$

Radivoje Đurić, 2015, Analogna Integrisana Kola

•The complete circuit

$\checkmark$  Rail-to-rail constant transconductance is only when the input pairs work in **weak inversion** region

✓ If the input pairs are in **strong inversion region**, the transconductance will change by a factor of 1.4 ( $\sqrt{2}$ )

✓ As working in weak inversion region is a requirement to get a rail-to-rail constant transconductance, this structure only applies to amplifiers with **low GBW**.

## **2.** Using square root circuit to keep $\sqrt{Ip} + \sqrt{In}$ constant

Basic idea:

•For an input differential pair, using a 1st order approximation

$$gm = \sqrt{2K_P(W/L)I_D} = \sqrt{K_P(W/L)I_{TAIL}}$$

Where the  $I_{TAIL}$  is the tail current of the differential pair. We can change gm by altering the tail current of the differential pair!

•The total transconductance of the input stage is given by

$$gm_{T} = gm_{N} + gm_{P} = \sqrt{KP_{N}(W/L)_{N}I_{N}} + \sqrt{KP_{P}(W/L)_{P}I_{P}}$$

If  $KP_{N}(W/L)_{N} = KP_{P}(W/L)_{P} = 2K$   $gm_{T} = gm_{N} + gm_{P} = \sqrt{2K}(\sqrt{I_{N}} + \sqrt{I_{P}})$

•To keep  $g_{mT}$  contant, we just need to keep  $\sqrt{Ip} + \sqrt{In}$  constant

Radivoje Đurić, 2015, Analogna Integrisana Kola

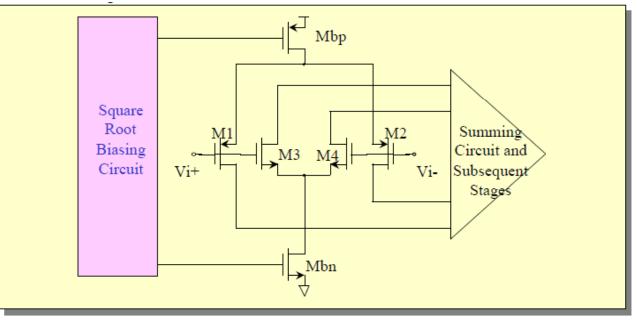

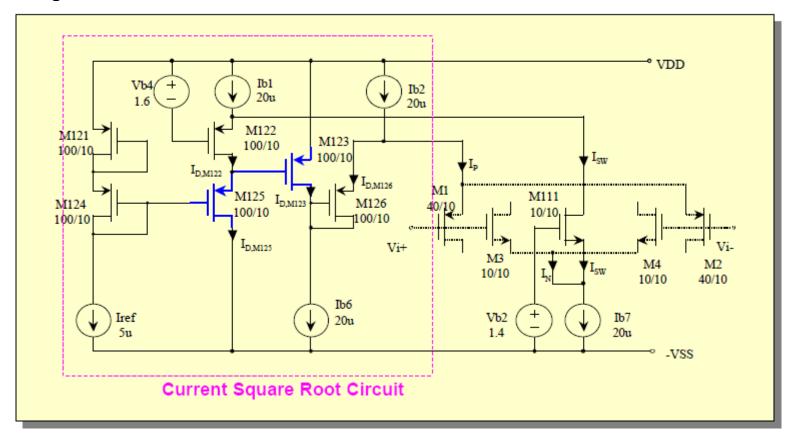

•We can utilize the square law characteristic of MOS transistors to implement the square root biasing circuit. The following is one implementation of the rail-to-rail input stage with square root biasing circuit.

Analysis:

1.

$$V_{SG,M123} + V_{SG,M125} = V_{SG,M121} + V_{SG,M124} = const$$

,

$V_{SG} = \sqrt{\frac{2I_D}{KP_P(W/L)}} + |V_{TP}|$ , as  $(W/L)_{M125} = (W/L)_{M123} = (W/L)_{M125,123}$ ,

Radivoje Đurić, 2015, Analogna Integrisana Kola

$$\sqrt{\frac{2I_{D,M123}}{KP_P(W/L)_{M123,125}}} + |V_{TP}| + \sqrt{\frac{2I_{D,M125}}{KP_P(W/L)_{M123,125}}} + |V_{TP}| = const$$

$$\sqrt{I_{D,M123}} + \sqrt{I_{D,M125}} = const_2$$

2. I<sub>N</sub>+I<sub>SW</sub>=I<sub>b7</sub>=I<sub>b</sub>, I<sub>D,M122</sub>+ I<sub>SW</sub>= I<sub>b1</sub>=I<sub>b</sub>, and I<sub>D,M122</sub>= I<sub>D,M125</sub>  $\rightarrow$  I<sub>N</sub>= I<sub>D,M125</sub>

3. I<sub>D,M123</sub>+ I<sub>D,M126</sub>= I<sub>b6</sub>=I<sub>b</sub>, I<sub>D,M126</sub>+ I<sub>P</sub>= I<sub>b2</sub>=I<sub>b</sub>,  $\rightarrow$  I<sub>P</sub>= I<sub>D,M123</sub>

From 1. to 3., we can obtain  $\sqrt{I_N} + \sqrt{I_P} = const_2$

If M121~M124 are with the same geometry, further calculation yields

$$\sqrt{I_N} + \sqrt{I_P} = 2\sqrt{I_{D,M121,124}} = 2\sqrt{I_{ref}}$$

Working Principle:

✓ The input transistors work in strong inversion region

$\checkmark$  The square-root circuit M121-M125 keeps the sum of the square-roots of the tail currents of the input pairs and then the gm constant.

✓The current switch, M111, compares the common-mode input voltage with Vb3 and decides which part of the current lb7 should be diverted to the square-root circuit.

✓ In the common-mode input voltage range from Vdd to -Vss+1.8V only the N channel pair operates. The current switch M111 is off and thus the tail current of the N channel input pair IN equals Ib7=4Iref=20uA.

✓The sum of the gate-source voltages of M123 and M125 is equal to reference voltage which is realized by M121 and M124. Since the current through M125 equals IN and the current through M123 equals the tail current of the P channel input pair IP. ✓ It can be calculated that the square-root of Ip is given by (M121-M125 matched)

$$\sqrt{I_P} = 2\sqrt{I_{ref}} - \sqrt{I_N}$$

✓ In the common-mode input range from -Vss+1.2V to Vss only the P channel input pair operates. In this range the current Ib7=4Iref=20uA flows through the current switch to the square-root circuit. Thus, the current through M125 is nearly zero which means that its gate-source voltage is smaller than its threshold voltage.

✓ If the current through M123 is larger than 4Iref=20uA, the current limiter M126 limits the current of M123 to 4Iref=20uA and directs it to the P channel input pair.

✓ It can be calculated that the transconductance of the input stage, and therefore the unitygain frequency, is constant within the rail-to-rail input common mode range. The gm is defined by  $-\frac{1}{2} + \frac{1}{2} +$

$$gm = 2\sqrt{2KIref}$$

where  $K = \frac{1}{2}KP_N(\frac{W}{L})_N = \frac{1}{2}KP_P(\frac{W}{L})_P$

$\checkmark$  The summing circuit adds the output signals of the complementary input stage, and forms the output voltage.

Discussion:

•The circuit is somewhat complex and the functionality relies on the square law of MOS transistors. For current sub-micron processes, the square law is not closely followed, which may introduce large error for the total transconductance.

### 3. Using current switches to change the tail current of input differential pairs

#### Basic idea

•We know that, by first order approximation, for a MOS transistor working in strong inversion and saturation region, square law applies, that is

$$I_{D} = K(V_{GS} - V_{T})^{2}$$

, and  $gm = 2\sqrt{KI_{D}}$ ,  $K = \frac{1}{2}KP(\frac{W}{L})$

•Suppose for the N and P input pairs,

$$KP_N(\frac{W}{L})_N = KP_P(\frac{W}{L})_P = 2K$$

and the tail currents of N and P pairs are equal, with the value of Itail

•When the input common mode voltage is in the mid-range, both of N and P pairs are conducting, so the total transconductance is

$$gm_T = gm_N + gm_P = 2\sqrt{2KI_{TAIL}}$$

•When the input common mode voltage is close to Vdd, the N pair operates. And when it is close to the -Vss, the P pair operates. In both cases, the total transconductance is only **half of that when both of N and P** pairs operate.

$$gm_T = gm_N = gm_P = \sqrt{2KI_{TAIL}}$$

•We can increase the tail current to **4 times of its original value to have the** same transconductance as that when both of N and P pairs operate.

•Increase the bias current in the differential amplifier that is on when the other differential amplifier is off.

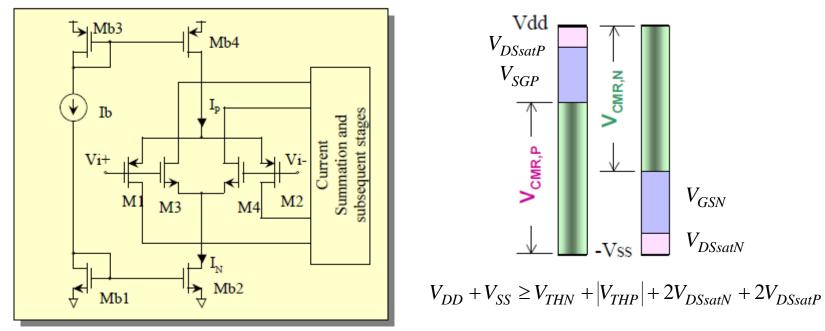

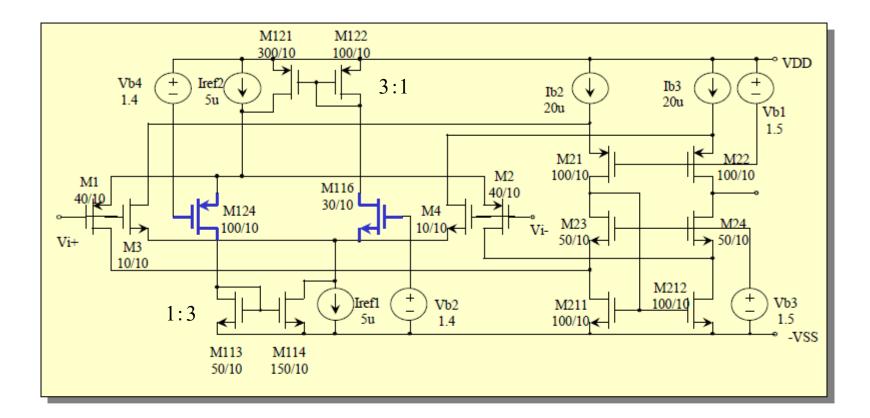

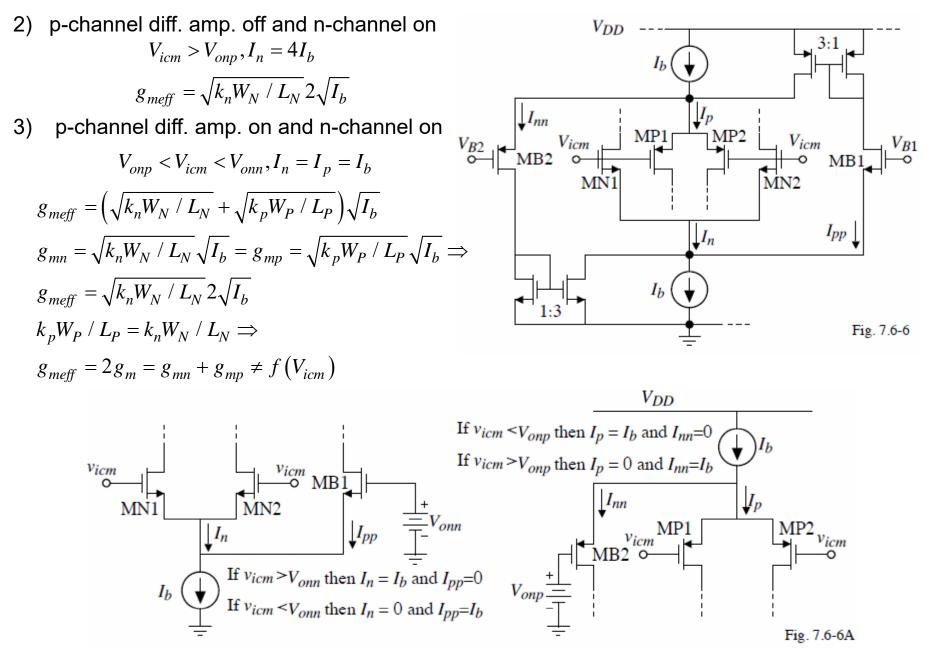

•Three regions of operation depending on the value of Vicm:

1) n-channel diff. amp. off and p-channel on

$$V_{icm} < V_{onn}, I_p = 4I_b$$

$$g_{meff} = \sqrt{k_p W_P / L_P} 2\sqrt{I_b}$$

Radivoje Đurić, 2015, Analogna Integrisana Kola

Radivoje Đurić, 2015, Analogna Integrisana Kola

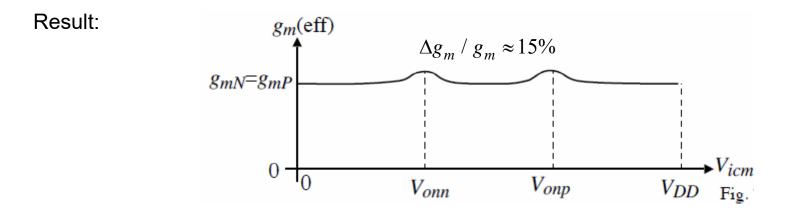

•If the common mode input voltage is between Vss+1.3V and Vss+1.5V, the M116 is partly conducting, and the rest of tail current flows through M3 and M4, which is assumed to be Ix here. So the tail current of the P pair is Iref+3(Iref-Ix).

•The total gm of the input stage is given by

$$gm_T = \sqrt{2K} (\sqrt{Ix} + \sqrt{Iref + 3(Iref - Ix)})$$

•Calculate the maximum value of this equation, we can obtain that when Ix=(1/3)Iref, gmT has its maximum value. Which yields

$$gm_T = \sqrt{2KIref} \left(\sqrt{\frac{1}{3}} + \sqrt{3}\right) = 2.31\sqrt{2KIref} = 2\sqrt{2KIref} (1 + 15.5\%)$$

Which is about 15% larger than its nominal value  $2\sqrt{2KIref}$ .

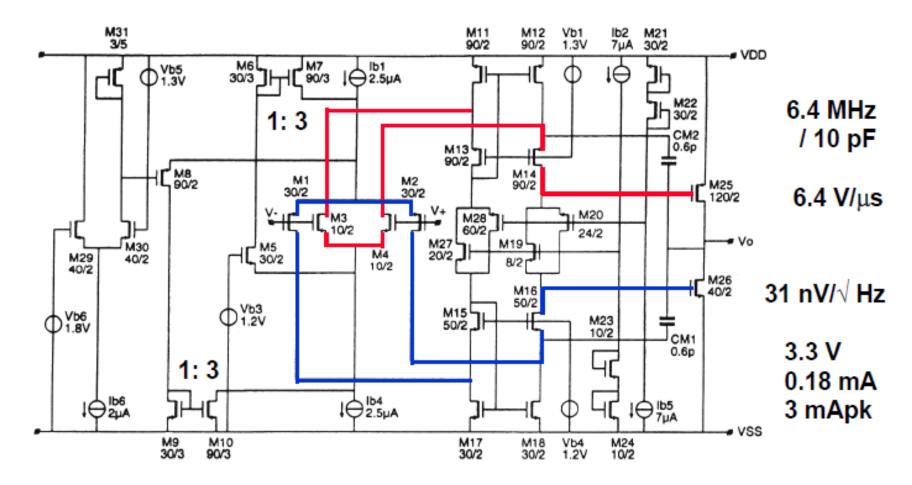

R. Hogervorst, J. P. Tero, R. G. H. Eschauzier, and J. H. Huijsing, A compact power-efficient 3 V CMOS rail-to-rail input/output operational amplifier for VLSI cell libraries, IEEE Journal of Solid-State Circuits, vol. 29, pp. 1505 – 1513, Dec. 1994.

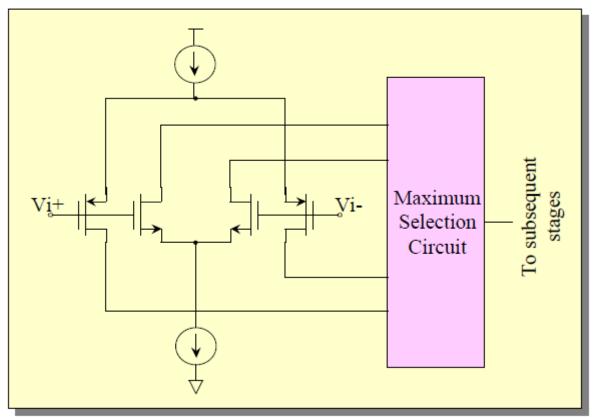

## 4. Using Maximum/Minimum selection circuit

The basic idea:

•From previous analysis, we know that, when the common mode voltage drives the tail current transistor out of saturation region, the tail current of a differential pair decreases dramatically with the common mode voltage.

•The differential pair, whichever it is N pair or P pair, with the larger current should be working properly. We just try to choose the pair with larger working current, and discard the output of another pair.

Radivoje Đurić, 2015, Analogna Integrisana Kola

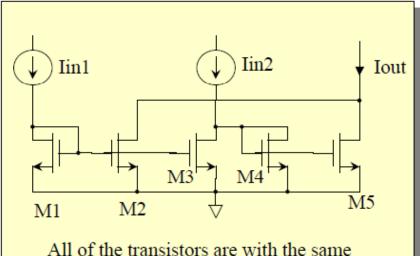

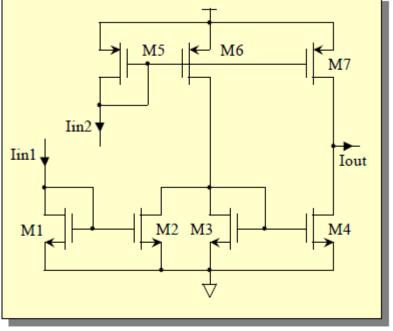

Maximum Current Selection Circuit:

•When lin1>lin2, M2 and M3 try to mirror lin1, but as lin2<lin1, there is no enough current for M3 to sink, M3 will work in Ohmic region and its VDS is very small. M4 and M5 are off. So lout = lin1 •When lin2>lin1,  $I_{D2}=I_{D3}=lin1$ ,  $I_{D4}=I_{D5}=lin2-lin1$ . lout = $I_{D5}+I_{D2}=lin1+(lin2-lin1)=lin2$

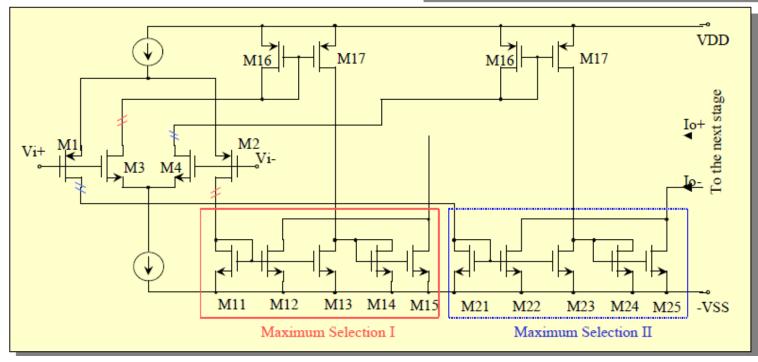

•The whole input stage

All of the transistors are with the same geometry.

Radivoje Đurić, 2015, Analogna Integrisana Kola

Working Principle:

•Please notice that if we apply a positive differential voltage to the inputs Vi+ and Vi-, the currents of M1 ( P type ) and M4 ( N type ) will decrease, and the currents of M2 ( P type ) and M3 ( N type ) will increase. We apply the current of M2 and mirrored current of M3 to Maximum Selection Circuit I, and current of M1 and the mirrored current of M4 to Maximum Selection Circuit II.

When the common mode input voltage is close to Vdd, the tail current of the P input pair decreases, the maximum selection circuits conduct the drain currents of N pair to the outputs.

When the common mode input voltage is close to -Vss, the tail current of the N input pair decreases, the maximum selection circuits conduct the drain currents of P pair to the outputs.

At the outputs, we get the larger currents of the 2 input pairs, and hence the larger gm.

•Transconductance vs. input common mode voltage:

Radivoje Đurić, 2015, Analogna Integrisana Kola

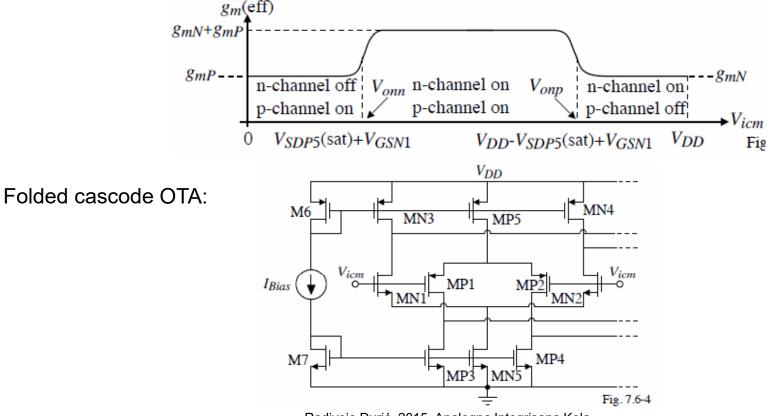

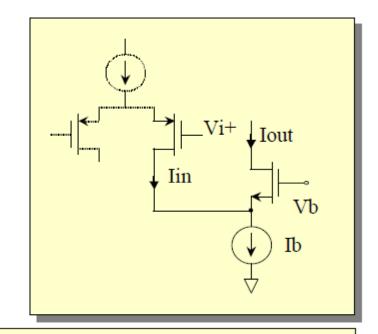

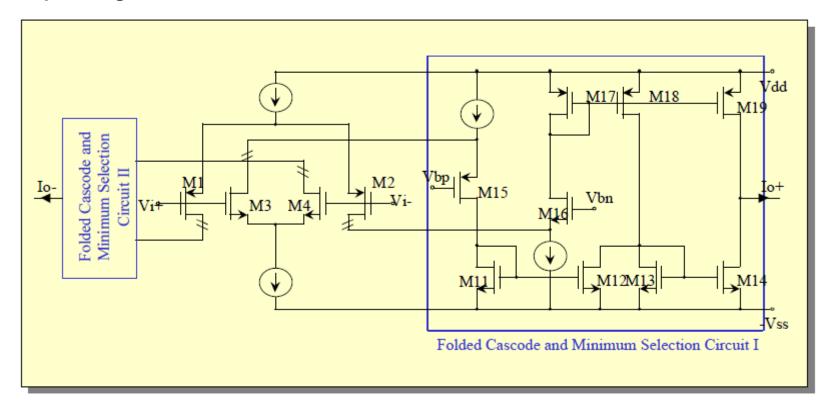

•There is another configuration which utilizes folded cacode circuit and minimum selection circuit to get the maximum gm.

•As in the folded cascoded shown in the next circuit, if lin is at it maximum value, we will get a minimum lout. So with this folded cascode circuit, we can not use maximum selection circuit, instead, we should use minimum selection circuit.

### •The minimum selection circuit:

$\checkmark$ As shown in the right circuit, all N transistors are with the same geometry, and P transistors are with the same geometry.

✓ If lin2<lin1,  $I_{D5}=I_{D6}=I_{D7}=lin2$ , M2 works in ohmic region, and M3 and M4 are off. lout=  $I_{D7}=lin2$ . ✓ If lin1<lin2,  $I_{D5}=I_{D6}=I_{D7}=lin2$ ,  $I_{D1}=I_{D2}=lin1$ ,  $I_{D3}=I_{D4}=lin2-lin1$ , lout=  $I_{D7}-I_{D4}=lin2-(lin2-lin1)=lin1$ .

•The input stage with folded cascode and minimum selection circuit: